Real-time capture and fast packet processing technology of high-speed network (10Gbps-100Gbps) is of great significance for network security analysis. Currently, single-core CPUs have limited real-time processing and analysis capabilities for network packets. High-speed network traffic often uses load-balancing technology and the packets are processed in parallel by multiple cores. At present, load balancing is mostly implemented by software, which is difficult to process high-speed data streams and introduces large delays.

Other hardware implementations either have difficulty in achieving sufficient performance or lack of flexible configuring the function of its ASIC (Application Specific Integrated Circuit) customization. What's more, High-speed network packet processing is difficult to reach line rate. As a result, the applications of these hardware implementations are limited.

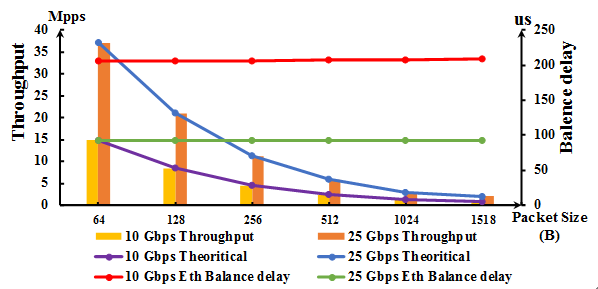

In order to solve these problems, Ph.D. ZHAO Jun, Professor GUO Zhichuan, Professor ZENG Xuewen, and Assistant Professor SONG Mangu of National Network New Media Engineering Research Center, Institute of Acoustics, Chinese Academy of Sciences (IACAS) proposed CRC32 algorithm based on the network packet's five-tuple information and implemented the hardware load balancing system on FPGA (Field Programmable Gate Array). FPGA could receive data packets at high speed, process 10Gbps or 25Gbps data in a single path, and distribute the data to each CPU core of the server at line rate. It has flexible configuration and low latency. In addition, the same service is assigned to the same core, which reduces the software processing of cross-core operations for the same service. So it could improve system performance.

The research was recently published in international journal IEEE Communications Magazine (IF = 10.356).

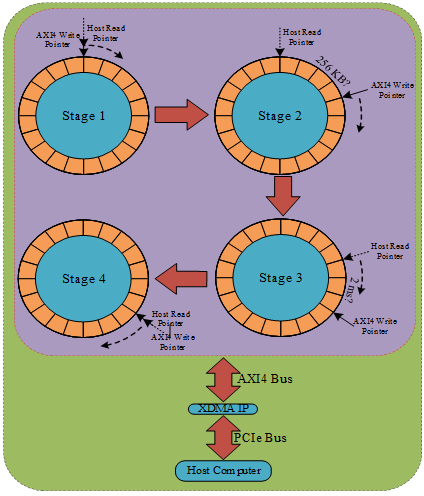

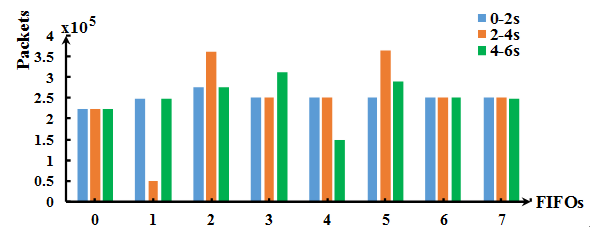

Researchers used FPGA to design modules such as high-speed Ethernet packet receiving, hardware load balancing, multiple FIFO and DDR4 AXI4 modules, high-speed XDMA, and high-performance Linux drivers. The system showed high speed, low latency, line rate, good balance performance, and flexible configuration specialty.

This method has a good application prospect in real-time data capture and security analysis of high-speed network.

Figure 1 Packet transferring process (Image by IACAS)

Figure 2 Number of packets distributed to FIFOs by load balancing (Image by IACAS)

Figure 3 System performance (Image by IACAS)

Reference:

ZHAO Jun, GUO Zhichuan, ZENG Xuewen, SONG Mangu, High-Performance Implementation of Dynamically Configurable Load Balancing Engine on FPGA, IEEE Communications Magazine, vol. 58, no. 1, pp. 62-67, January 2020. DOI: 10.1109/MCOM.001.1900525

Contact:

ZHOU Wenjia

Institute of Acoustics, Chinese Academy of Sciences, 100190 Beijing, China

E-mail: media@mail.ioa.ac.cn