As the complexity of System-on-Chips (SoCs) increases, testing such large circuits is a challenge due to some limited factors, such as volume of the test data, long test application time, high power consumption during test and limited Automatic Test Equipment (ATE) bandwidth. And test data compression (TDC) is one of most effective techniques in terms of reducing test application time and memory requirement.

Extensive work has been done on the code-based schemes to compress the precomputed test data set usually provided by core vendor to a smaller test set which is then stored in the ATE’s memory. However, this scheme always requires a low overhead on-chip decoder when compressed data is applied to the circuit under test.

A novel pattern run-length coding method is presented in this research for improving the performance of TDC. The test set is divided to several patterns with 2n selected as the pattern length. And then, the external compatibility type and internal compatibility type are analyzed. Besides, a backtracking-X-assigning technique is used to keep the value of X-bits consistent in the analysis process. At last, the codeword for each pattern is generated according to the coding rules. Different codeword corresponding to different types are proposed to reach a compression ratio as high as possible.

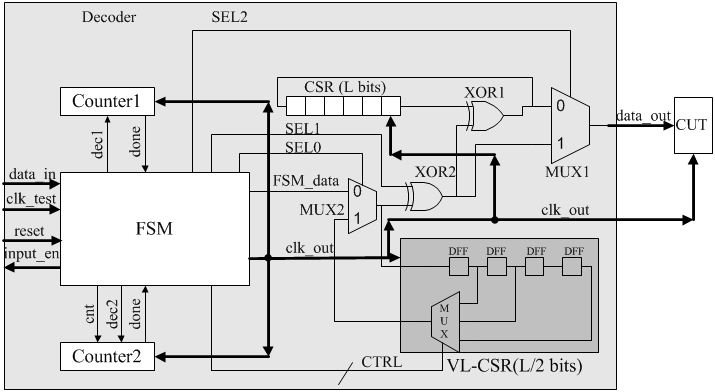

Fig.1. The Decoder Architechture

As shown in Fig.1, the decoder for the proposed coding method comprises a finite state machine, a cyclical shift register (CSR) used to store the external common pattern, a variable-length CSR (VL-CSR) used to store the internal common pattern, two XOR gates, two counters and two 2-1 multiplexers. The CSR comprises 2n registers while the VL-CSR comprises 2n-1 registers and an n-1 MUX which can select the output of which register to feedback according to its input.

Experimental results on ISCAS89 benchmarks show the superiority of proposed coding method over other known schemes, and the corresponding decoder based on CSR and VL-CSR with a low hardware overhead proves that it is applicable in SoCs.

The research entitled “A Novel Pattern Run-Length Coding Method for Test Data Compression” has been released in IEICE Transactions on Electronics (VOL.E96-C, NO.9 September, 2013). It can be searched through the website:http://search.ieice.org/bin/summary.php?id=e96-c_9_1201&category=C&year=2013&lang=E&abst.

Corresponding author:

Wu Diancheng

Institute of Acoustics, Chinese Academy of Sciences, Beijing, 100190, China

Email: wudiancheng@mail.ioa.ac.cn