Phase Change Memory (PCM), next-generation memory system, has longer write latency and higher write power.

This character raises significant challenge in enabling real adoption of PCM. Previous researchers have shown removing all writes can improve performance by 39.0% on average.

Therefore, improving write performance is critical for PCM memory system.

PCM write is a power-intensive operation. Besides, PCM write power is asymmetric: writing a zero consumes more power than writing a one.

For PCM memory, the number of write commands that can be served concurrently is limited, due to maximum power constraint. That is called write commands parallelism.

Previous presented Power-token is to improve write commands parallelism without violating the power constraint. However, Power-token disregards the power asymmetry of writing a zero and writing a one, and thus limits write commands parallelism.

A new scheduling policy, write power asymmetry scheduling, has been proposed to improve write commands parallelism, by researchers from the Institute of Acoustics of the Chinese Academy of Sciences.

Instead of assuming all of the modified bits are zeros as Power-token does, write power asymmetry scheduling calculates the power consumption of every write command considering the write power asymmetry.

Since writing a one consumes less power than writing a zero and large number of modified bits is ones, write power asymmetry scheduling can issue more writes than Power-token under the same power constraint.

It improves write commands parallelism, and thus improves PCM memory performance.

Sub-rank memory, which divides a large rank into multiple small ranks, is a common architecture to improve parallelism. Applying write power asymmetry scheduling to the sub-rank memory, hereafter abbreviated as WPAS-S, can further improve PCM memory system performance.

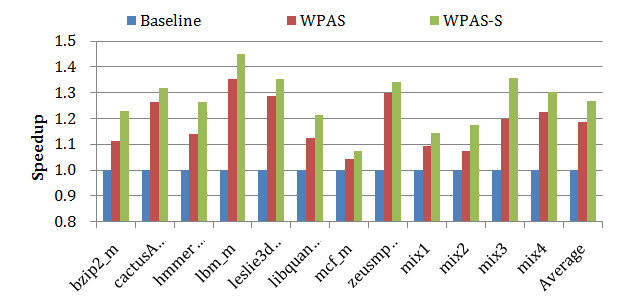

Fig. 1 shows performance improvements of write power asymmetry scheduling and WPAS-S over the baseline Power-token technique.

Write power asymmetry scheduling can improve PCM memory system performance by up to 35.5%, and 18.5% on average. WPAS-S can further improve performance by 8.4% on average, compared with write power asymmetry scheduling.

The latency, area, and power overheads of write power asymmetry scheduling are also evaluated. The result shows that the implementation overheads are low and acceptable in practice.

Fig. 1. Execution time speedup. WPAS: write power asymmetry scheduling; WPAS-S: applying write power asymmetry scheduling to the sub-rank memory (Image by WANG).

References:

WANG Qi, WANG Donghui, HOU Chaohuan. Exploiting write power asymmetry to improve phase change memory system performance. Frontiers of Computer Science. March. 2015. ISSN 2095-2236. DOI 10.1007/s11704-014-4185-4

Contact:

WANG Qi

Institute of Acoustics, Chinese Academy of Sciences, 100190 Beijing, China

Email: qi0104@126.com